Difference between revisions of "Minimig Board v1.0 RAM connections"

Jump to navigation

Jump to search

(+img) |

(layout + clarification) |

||

| Line 1: | Line 1: | ||

<!-- perl -ne '/^(\S+)\t(\S*)/s; printf("|-\n| %3d || %s || %s\n",++$n,$1,$2);' < ram0_pins.txt | more --> | <!-- perl -ne '/^(\S+)\t(\S*)/s; printf("|-\n| %3d || %s || %s\n",++$n,$1,$2);' < ram0_pins.txt | more --> | ||

| − | IC7 - M68AW512M RAM Bank #0 512K*16<br> | + | IC7 - M68AW512M RAM Bank #0 512K*16 (Asynchronous SRAM)<br> |

{| class="wikitable" | {| class="wikitable" | ||

|- | |- | ||

| Line 94: | Line 94: | ||

|} | |} | ||

| − | IC6 - M68AW512M RAM Bank #1 512K*16<br> | + | IC6 - M68AW512M RAM Bank #1 512K*16 (Asynchronous SRAM)<br> |

{| class="wikitable" | {| class="wikitable" | ||

|- | |- | ||

| Line 102: | Line 102: | ||

|} | |} | ||

| − | [[Image:Minimig_v10_board_ram512x16.png| | + | [[Image:Minimig_v10_board_ram512x16.png| none |right|250px|IC6/IC7 - [[Asynchronous static ram]] 512 x 16 bit (2 chips)]] |

| + | |||

| + | This chip is no longer available. | ||

Revision as of 17:11, 24 August 2007

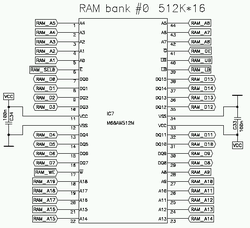

IC7 - M68AW512M RAM Bank #0 512K*16 (Asynchronous SRAM)

| Pin | Name | Assignment | Comment |

|---|---|---|---|

| 1 | A4 | RAM_A5 | |

| 2 | A3 | RAM_A4 | |

| 3 | A2 | RAM_A3 | |

| 4 | A1 | RAM_A2 | |

| 5 | A0 | RAM_A1 | |

| 6 | nE | nRAM_SEL0 | Selection (CS) |

| 7 | DQ0 | RAM_D0 | |

| 8 | DQ1 | RAM_D1 | |

| 9 | DQ2 | RAM_D2 | |

| 10 | DQ3 | RAM_D3 | |

| 11 | Vcc | ||

| 12 | Vss | GND | |

| 13 | DQ4 | RAM_D4 | |

| 14 | DQ5 | RAM_D5 | |

| 15 | DQ6 | RAM_D6 | |

| 16 | DQ7 | RAM_D7 | |

| 17 | nW | nRAM_WE | Write enable |

| 18 | A18 | RAM_A19 | |

| 19 | A17 | RAM_A18 | |

| 20 | A16 | RAM_A17 | |

| 21 | A15 | RAM_A16 | |

| 22 | A14 | RAM_A15 | |

| 23 | A13 | RAM_A14 | |

| 24 | A12 | RAM_A13 | |

| 25 | A11 | RAM_A12 | |

| 26 | A10 | RAM_A11 | |

| 27 | A9 | RAM_A10 | |

| 28 | A8 | RAM_A9 | |

| 29 | DQ8 | RAM_D8 | |

| 30 | DQ9 | RAM_D9 | |

| 31 | DQ10 | RAM_D10 | |

| 32 | DQ11 | RAM_D11 | |

| 33 | Vcc | ||

| 34 | Vss | GND | |

| 35 | DQ12 | RAM_D12 | |

| 36 | DQ13 | RAM_D13 | |

| 37 | DQ14 | RAM_D14 | |

| 38 | DQ15 | RAM_D15 | |

| 39 | nLB | nRAM_LB | Lower byte |

| 40 | nUB | nRAM_UB | Upper byte |

| 41 | nG | nRAM_OE | Output enable |

| 42 | A7 | RAM_A8 | |

| 43 | A6 | RAM_A7 | |

| 44 | A5 | RAM_A6 |

IC6 - M68AW512M RAM Bank #1 512K*16 (Asynchronous SRAM)

| Pin | Name | Assignment | Comment |

|---|---|---|---|

| 6 | nE | nRAM_SEL1 |

This chip is no longer available.