Difference between revisions of "Minimig Board v1.0 schematic"

Jump to navigation

Jump to search

(additional data) |

(cleanup) |

||

| (One intermediate revision by the same user not shown) | |||

| Line 1: | Line 1: | ||

| − | Board schematic for Minimig board v1.0 | + | Board schematic for Minimig board v1.0: |

[[Image:Minimig_v10_board_audio.png|thumb|right|250px|J1 - Audio output via 3,5mm jack]] | [[Image:Minimig_v10_board_audio.png|thumb|right|250px|J1 - Audio output via 3,5mm jack]] | ||

| − | |||

| − | |||

| − | |||

| − | |||

[[Image:Minimig_v10_board_dac.png|thumb|right|250px|J4 - 4 bit resistor ladder D/A]] | [[Image:Minimig_v10_board_dac.png|thumb|right|250px|J4 - 4 bit resistor ladder D/A]] | ||

| − | + | In 15kHz mode: | |

| − | |||

:/VSYNC = high (scart RGB enable) | :/VSYNC = high (scart RGB enable) | ||

:/HSYNC = composite sync | :/HSYNC = composite sync | ||

[[Image:Minimig_v10_board_fpga.png|thumb|right|250px|IC5 - [[FPGA]] Xilinx XC3S400-4PQ208C]] | [[Image:Minimig_v10_board_fpga.png|thumb|right|250px|IC5 - [[FPGA]] Xilinx XC3S400-4PQ208C]] | ||

| − | |||

[[Image:Minimig_v10_board_fpga_core_pwr.png|thumb|right|250px|IC3/IC4 - FPGA core power +1,25V +2,5V using [http://www.national.com/pf/LM/LM1117.html LM1117MP-ADJ] ]] | [[Image:Minimig_v10_board_fpga_core_pwr.png|thumb|right|250px|IC3/IC4 - FPGA core power +1,25V +2,5V using [http://www.national.com/pf/LM/LM1117.html LM1117MP-ADJ] ]] | ||

| − | |||

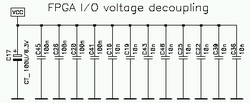

[[Image:Minimig_v10_board_fpga_decoupling.png|thumb|right|250px|FPGA [[decoupling]]]] | [[Image:Minimig_v10_board_fpga_decoupling.png|thumb|right|250px|FPGA [[decoupling]]]] | ||

[[Image:Minimig_v10_board_joy0.png|thumb|right|250px|J10 - Joystick 0]] | [[Image:Minimig_v10_board_joy0.png|thumb|right|250px|J10 - Joystick 0]] | ||

| Line 27: | Line 20: | ||

:Disconnect net SPI_DOUT from pin 81 of FPGA. | :Disconnect net SPI_DOUT from pin 81 of FPGA. | ||

:Connect net SPI_DOUT to pin 19 of FPGA (net USER3). | :Connect net SPI_DOUT to pin 19 of FPGA (net USER3). | ||

| − | + | :REASON: Pin 81 is an output during FPGA config that blocks SPI to MMC during startup. | |

| − | :REASON | ||

| − | :Pin 81 is an output during FPGA config that blocks SPI to MMC during startup. | ||

[[Image:Minimig_v10_board_pic18.png|thumb|right|250px|IC10 - [[MCU]] [http://ww1.microchip.com/downloads/en/devicedoc/39564b.pdf PIC18LF252I/SP] (DIP28)]] | [[Image:Minimig_v10_board_pic18.png|thumb|right|250px|IC10 - [[MCU]] [http://ww1.microchip.com/downloads/en/devicedoc/39564b.pdf PIC18LF252I/SP] (DIP28)]] | ||

| − | |||

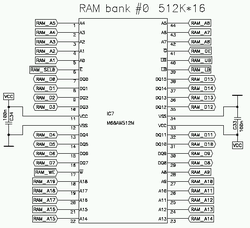

[[Image:Minimig_v10_board_ram512x16.png|thumb|right|250px|IC6/IC7 - [[Asynchronous static ram]] 512 x 16 bit (2 chips)]] | [[Image:Minimig_v10_board_ram512x16.png|thumb|right|250px|IC6/IC7 - [[Asynchronous static ram]] 512 x 16 bit (2 chips)]] | ||

| − | |||

[[Image:Minimig_v10_board_rs232.png|thumb|right|250px|IC2 - Serial [[RS232]] using [http://datasheets.maxim-ic.com/en/ds/MAX220-MAX249.pdf MAX232A] (SO16), output J3]] | [[Image:Minimig_v10_board_rs232.png|thumb|right|250px|IC2 - Serial [[RS232]] using [http://datasheets.maxim-ic.com/en/ds/MAX220-MAX249.pdf MAX232A] (SO16), output J3]] | ||

[[Image:Minimig_v10_board_main_pwr.png|thumb|right|250px|IC1 - Main power supply]] | [[Image:Minimig_v10_board_main_pwr.png|thumb|right|250px|IC1 - Main power supply]] | ||

| − | |||

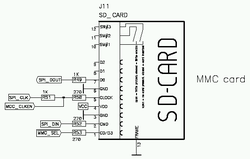

[[Image:Minimig_v10_board_sd_card.png|thumb|right|250px|J11 - [[SD Card]] slot]] | [[Image:Minimig_v10_board_sd_card.png|thumb|right|250px|J11 - [[SD Card]] slot]] | ||

[[Image:Minimig_v10_board_spare_io.png|thumb|right||J9 - Spare I/O directly connected to FPGA]]<br> | [[Image:Minimig_v10_board_spare_io.png|thumb|right||J9 - Spare I/O directly connected to FPGA]]<br> | ||

| − | |||

| − | |||

Latest revision as of 13:30, 7 August 2007

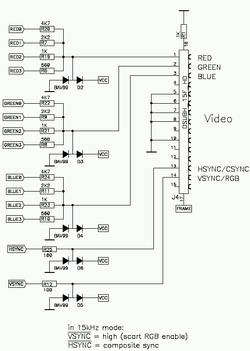

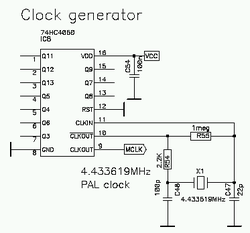

Board schematic for Minimig board v1.0:

In 15kHz mode:

- /VSYNC = high (scart RGB enable)

- /HSYNC = composite sync

IC5 - FPGA Xilinx XC3S400-4PQ208C

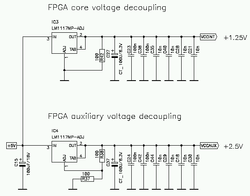

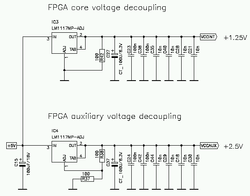

IC3/IC4 - FPGA core power +1,25V +2,5V using LM1117MP-ADJ

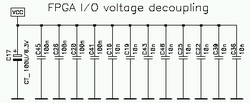

FPGA decoupling

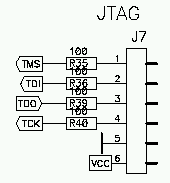

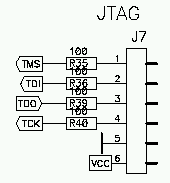

J7 - Jtag

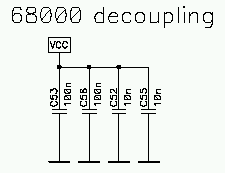

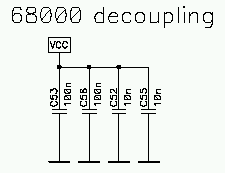

MC68000 Decoupling

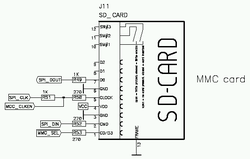

PATCH needed to get rev 1 board working:

- Disconnect net SPI_DOUT from pin 81 of FPGA.

- Connect net SPI_DOUT to pin 19 of FPGA (net USER3).

- REASON: Pin 81 is an output during FPGA config that blocks SPI to MMC during startup.

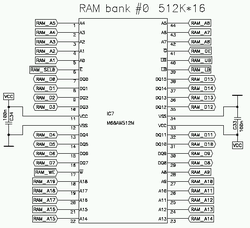

IC6/IC7 - Asynchronous static ram 512 x 16 bit (2 chips)

J11 - SD Card slot